# (19)中华人民共和国国家知识产权局

# (12)发明专利申请

(10)申请公布号 CN 109285845 A (43)申请公布日 2019.01.29

- (21)申请号 201811317754.4

- (22)申请日 2018.11.07

- (30)优先权数据

107127056 2018.08.03 TW

- (71)申请人 友达光电股份有限公司 地址 中国台湾新竹市

- (72)发明人 林宜欣 黄朝伟 陈正欣

- (74)专利代理机构 隆天知识产权代理有限公司 72003

代理人 黄艳

(51) Int.CI.

H01L 27/12(2006.01)

*H01L 21/77*(2017.01)

**H01L 27/15**(2006.01)

权利要求书2页 说明书10页 附图9页

### (54)发明名称

阵列基板、应用其的显示装置及该基板和装 置制造方法

#### (57)摘要

一种阵列基板,其包括第一线路板、第二线路板、粘着层以及至少一连接电极。第一线路板具有第一表面。第一线路板包括至少一第一接垫以及至少一第二接垫。第二线路板具有第二表面。第二线路板包括至少一压合接垫。粘着层位于第一线路板与第二线路板之间。第一线路板的第一边缘、第二线路板的第二边缘以及粘着层的粘着边缘基本上彼此切齐。连接电极从第一表面沿第一边缘、第二边缘以及粘着边缘延伸至第二表面。连接电极电性连接于第二接垫与压合接垫。

- 1.一种阵列基板,包括:

- 一第一线路板,具有一第一表面,且该第一线路板包括至少一第一接垫以及至少一第二接垫:

- 一第二线路板,具有一第二表面,且该第二线路板包括至少一压合接垫;

- 一粘着层,位于该第一线路板与该第二线路板之间,其中该第一线路板的一第一边缘、该第二线路板的一第二边缘以及该粘着层的一粘着边缘基本上彼此切齐;以及

至少一连接电极,从该第一线路板的该第一表面沿该第一线路板的该第一边缘、该第二线路板的该第二边缘以及该粘着层的该粘着边缘延伸至该第二线路板的该第二表面,且该至少一连接电极电性连接于该至少一第二接垫与该至少一压合接垫。

- 2.如权利要求1所述的阵列基板,其中该第一线路板的该第一边缘、该第二线路板的该 第二边缘以及该粘着层的该粘着边缘构成一平整面,且该至少一连接电极至少部分覆盖于 该平整面上。

- 3. 如权利要求1所述的阵列基板,其中该粘着层的厚度小于或等于10微米。

- 4. 如权利要求1所述的阵列基板,还包括:

- 一电极保护层,覆盖于该至少一连接电极上。

- 5. 如权利要求1所述的阵列基板,还包括:

- 一第一保护层,覆盖于该第一线路板上,该第一保护层具有至少一第一导通孔,且该至少一连接电极通过该至少一第一导通孔电性连接于该至少一第二接垫。

- 6.如权利要求5所述的阵列基板,其中该第一保护层具有对应于该至少一第一接垫的至少一第一开口以及对应于该至少一第二接垫的至少一第二开口。

- 7. 如权利要求1所述的阵列基板,还包括:

- 一第二保护层,覆盖于该第二线路板上,该第二保护层具有至少一第二导通孔,且该至少一连接电极通过该至少一第二导通孔电性连接于该至少一压合接垫。

- 8. 如权利要求7所述的阵列基板,其中该第二保护层具有对应于该至少一压合接垫的至少一压合开口。

- 9.一种显示装置,包括:

如权利要求1的阵列基板:以及

至少一微型发光元件,配置于该阵列基板上,该至少一微型发光元件电性连接于该至少一第一接垫以及该至少一第二接垫。

- 10. 如权利要求9所述的显示装置,还包括:

- 一电路板,电性连接于该至少一压合接垫。

- 11.一种阵列基板的制造方法,包括:

提供一第一线路板,该第一线路板包括至少一第一接垫以及至少一第二接垫;

提供一第二线路板,该第二线路板包括至少一压合接垫;

进行一粘合工艺,以形成粘合该第一线路板与该第二线路板的一粘着层;

进行一切割工艺,以切割该第一线路板、该粘着层以及该第二线路板的至少其中之一; 以及

于进行该切割工艺之后,形成至少一连接电极,以电性连接该至少一第二接垫与该至少一压合接垫,该至少一连接电极至少部分覆盖该第一线路板的一第一边缘、该第二线路

板的一第二边缘以及该粘着层的一粘着边缘,且该第一线路板的该第一边缘、该第二线路板的该第二边缘以及该粘着层的该粘着边缘基本上彼此切齐。

- 12. 如权利要求11所述的阵列基板的制造方法,其中该第一线路板的该第一边缘、该第二线路板的该第二边缘以及该粘着层的该粘着边缘构成一平整面,且该至少一连接电极至少部分覆盖于该平整面上。

- 13.如权利要求11所述的阵列基板的制造方法,其中该粘着层的厚度小于或等于10微米。

- 14. 如权利要求11所述的阵列基板的制造方法,还包括:

形成一电极保护层于该至少一连接电极上。

- 15. 如权利要求11所述的阵列基板的制造方法,还包括:

- 于进行该切割工艺之前,于该第一线路板上形成一第一保护层。

- 16. 如权利要求11所述的阵列基板的制造方法,还包括:

- 于进行该切割工艺之前,于该第二线路板上形成一第二保护层。

- 17.一种显示装置的制造方法,包括:

提供如权利要求1的阵列基板;以及

配置至少一微型发光元件于该阵列基板上,且该至少一微型发光元件电性连接于该至少一第一接垫以及该至少一第二接垫。

# 阵列基板、应用其的显示装置及该基板和装置制造方法

### 技术领域

[0001] 本发明涉及一种电子装置及其制造方法,且特别涉及一种阵列基板及其制造方法,及应用此阵列基板的显示装置及其制造方法。

# 背景技术

[0002] 在阵列基板的工艺中,于一素基板 (bare substrate) 相对的两个面皆形成电子元件在工艺上较为复杂。并且,只要其中一个面的电子元件损坏,则不论另一个面的电子元件是否损坏,整个阵列基板即造成损坏。

# 发明内容

[0003] 本发明提供一种阵列基板及其制造方法,其制造方法较为简单,且具有较佳的制作良率。

[0004] 本发明的阵列基板包括第一线路板、第二线路板、粘着层以及至少一连接电极。第一线路板具有第一表面。第一线路板包括至少一第一接垫以及至少一第二接垫。第二线路板具有第二表面。第二线路板包括至少一压合接垫。粘着层位于第一线路板与第二线路板之间。第一线路板的第一边缘、第二线路板的第二边缘以及粘着层的粘着边缘基本上彼此切齐。连接电极从第一线路板的第一表面沿第一线路板的第一边缘、第二线路板的第二边缘以及粘着层的粘着边缘延伸至第二线路板的第二表面。连接电极电性连接于第二接垫与压合接垫。

[0005] 本发明的阵列基板的制造方法包括以下步骤。提供第一线路板。第一线路板包括至少一第一接垫以及至少一第二接垫。提供第二线路板。第二线路板包括至少一压合接垫。进行粘合工艺,以形成粘合第一线路板与第二线路板的粘着层。进行切割工艺,以切割第一线路板、粘着层以及第二线路板的至少其中之一。于进行切割工艺之后,形成至少一连接电极,以电性连接第二接垫与压合接垫。连接电极至少部分覆盖第一线路板的第一边缘、第二线路板的第二边缘以及粘着层的粘着边缘,且第一线路板的第一边缘、第二线路板的第二边缘以及粘着层的粘着边缘基本上彼此切齐。

[0006] 基于上述,本发明的阵列基板是通过粘着层将第一线路板与第二线路板彼此粘合。因此,阵列基板的制造方法较为简单。并且,可以在将第一线路板与第二线路板彼此粘合前确认第一线路板与第二线路板具有良好的功能。因此,可以提升阵列基板的制作良率。另外,用于将第一线路板与第二线路板彼此电性连接的连接电极是形成在第一线路板的第一边缘、第二线路板的第二边缘以及粘着层的粘着边缘上,而第一线路板的第一边缘、第二线路板的第二边缘以及粘着层的粘着边缘上可以通过切割工艺而基本上彼此切齐。因此,阵列基板的制造方法较为简单,且可以提升阵列基板的制作良率。

[0007] 本发明提供一种显示装置及其制造方法,其制造方法较为简单,且具有优选的制作良率。

[0008] 本发明的显示装置包括前述的阵列基板以及至少一微型发光元件。微型发光元件

配置于阵列基板上。微型发光元件电性连接于第一接垫以及第二接垫。

[0009] 本发明的显示装置的制造方法包括以下步骤。提供前述的阵列基板。配置至少一微型发光元件于阵列基板上。微型发光元件电性连接于第一接垫以及第二接垫。

[0010] 基于上述,本发明的显示装置是由本发明的阵列基板所构成。因此,显示装置的制造方法也可以较为简单,且具有优选的制作良率。

[0011] 为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合说明书附图作详细说明如下。如本领域技术人员将认识到的,可以以各种不同的方式修改所描述的实施例,而不脱离本发明的构思或范围。

[0012] 在附图中,为了清楚起见,放大了各元件等的厚度。在整个说明书中,相同的附图标记表示相同的元件。应当理解,当诸如层、膜、区域或基板的元件被称为在"另一元件上"、或"连接到另一元件"、"重叠于另一元件"时,其可以直接在另一元件上或与另一元件连接,或者中间元件可以也存在。相反,当元件被称为"直接在另一元件上"或"直接连接到"另一元件时,不存在中间元件。如本文所使用的,"连接"可以指物理及/或电连接。

[0013] 应当理解,尽管术语"第一"、"第二"、"第三"等在本文中可以用于描述各种元件、部件、区域、层及/或部分,但是这些元件、部件、区域、及/或部分不应受这些术语的限制。这些术语仅用于将一个元件、部件、区域、层或部分与另一个元件、部件、区域、层或部分区分开。因此,下面讨论的"第一元件"、"部件"、"区域"、"层"、或"部分"可以被称为第二元件、部件、区域、层或部分而不脱离本文的教导。

[0014] 这里使用的术语仅仅是为了描述特定实施例的目的,而不是限制性的。如本文所使用的,除非内容清楚地指示,否则单数形式"一"、"一个"和"该"旨在包括多个形式,包括"至少一"或"至少一个"。"或"表示"及/或"。如本文所使用的,术语"及/或"包括一个或多个相关所列项目的任何和所有组合。还应当理解,当在本说明书中使用时,术语"包括"及/或"包括"指定所述特征、区域、整体、步骤、操作、元件的存在及/或部件,但不排除一个或多个其它特征、区域整体、步骤、操作、元件、部件及/或其组合的存在或添加。

[0015] 此外,诸如"下"或"底部"和"上"或"顶部"的相对术语可在本文中用于描述一个元件与另一元件的关系,如图所示。应当理解,相对术语旨在包括除了图中所示的方位之外的装置的不同方位。例如,如果一个附图中的装置翻转,则被描述为在其他元件的"下"侧的元件将被定向在其他元件的"上"侧。因此,示例性术语"下"可以包括"下"和"上"的取向,取决于附图的特定取向。类似地,如果一个附图中的装置翻转,则被描述为在其它元件"下方"或"下方"的元件将被定向为在其它元件"上方"。因此,示例性术语"下面"或"下面"可以包括上方和下方的取向。

[0016] 本文使用的"约"、"实质上"、或"近似"包括所述值和在本领域普通技术人员确定的特定值的可接受的偏差范围内的平均值,考虑到所讨论的测量和与测量相关的误差的特定数量(即,测量系统的限制)。例如,"约"可以表示在所述值的一个或多个标准偏差内,或±30%、±20%、±10%、±5%内。

[0017] 除非另有定义,本文使用的所有术语(包括技术和科学术语)具有与本发明所属领域的普通技术人员通常理解的相同的含义。将进一步理解的是,诸如在通常使用的字典中定义的那些术语应当被解释为具有与它们在相关技术和本发明的上下文中的含义一致的含义,并且将不被解释为理想化的或过度正式的意义,除非本文中明确地这样定义。

[0018] 本文参考作为理想化实施例的示意图的截面图来描述示例性实施例。因此,可以预期到作为例如制造技术及/或公差的结果的图示的形状变化。因此,本文所述的实施例不应被解释为限于如本文所示的区域的特定形状,而是包括例如由制造导致的形状偏差。例如,示出或描述为平坦的区域通常可以具有粗糙及/或非线性特征。此外,所示的锐角可以是圆的。因此,图中所示的区域本质上是示意性的,并且它们的形状不是旨在示出区域的精确形状,并且不是旨在限制权利要求的范围。

## 附图说明

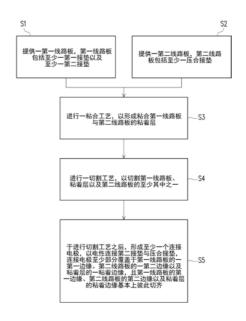

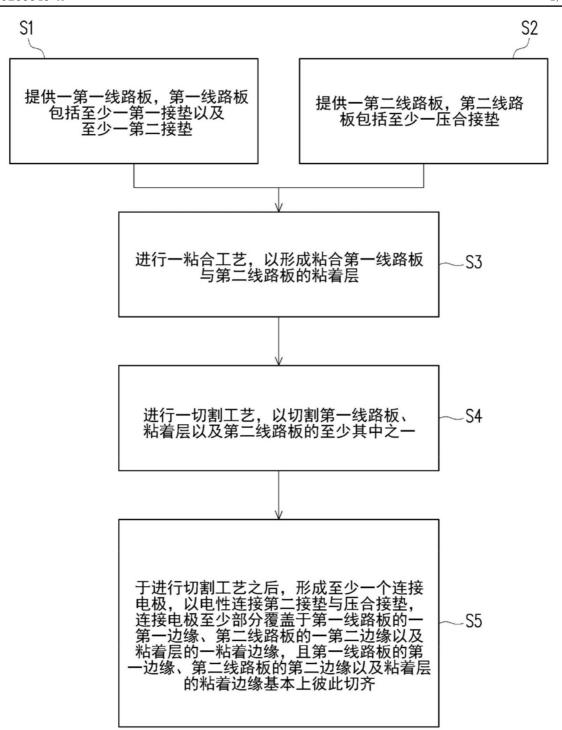

[0019] 图1A是依照本发明的第一实施例的一种阵列基板的制造方法的流程图。

[0020] 图1B至图1H是依照本发明的第一实施例的一种阵列基板的制造方法的部分剖面示意图。

[0021] 图11是依照本发明的第一实施例的一种阵列基板的部分制造方法的部分俯视图。

[0022] 图1J是依照本发明的第一实施例的一种阵列基板的部分制造方法的立体示意图。

[0023] 图2是依照本发明的第二实施例的一种阵列基板的部分剖面示意图。

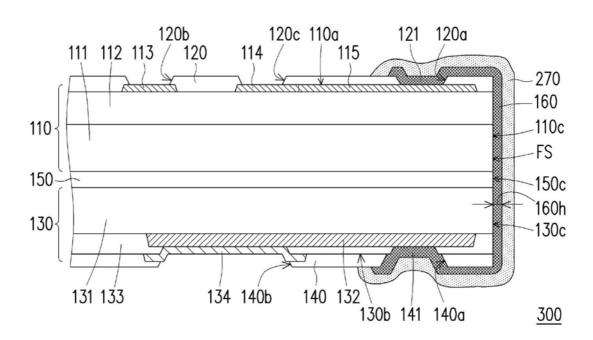

[0024] 图3是依照本发明的第三实施例的一种阵列基板的部分剖面示意图。

[0025] 图4是依照本发明的第四实施例的一种阵列基板的部分制造方法的立体示意图。

[0026] 图5是依照本发明的第五实施例的一种阵列基板的部分制造方法的立体示意图。

[0027] 图6是依照本发明的第六实施例的一种阵列基板的部分制造方法的立体示意图。

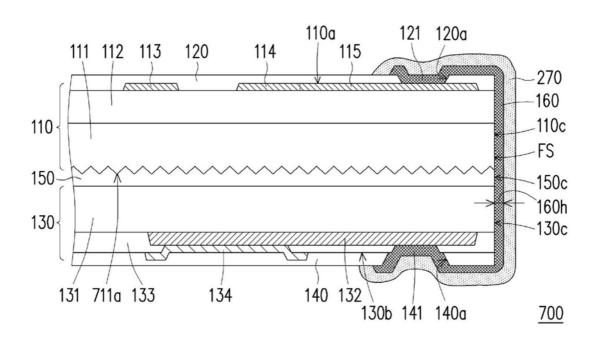

[0028] 图7是依照本发明的第七实施例的一种阵列基板的部分剖面示意图。

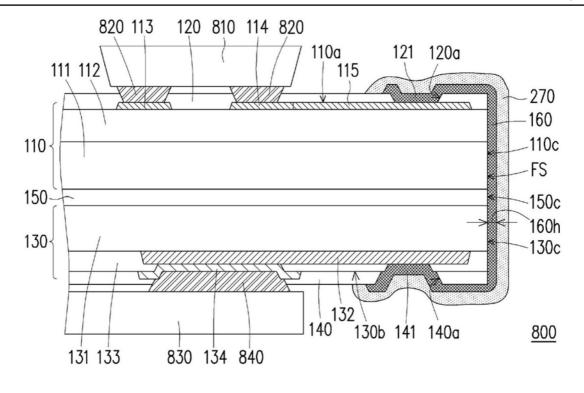

[0029] 图8是依照本发明的一种显示装置的部分剖面示意图。

[0030] 附图标记说明:

[0031] 100、200、300、700:阵列基板

[0032] 101:粘合结构

[0033] 110:第一线路板

[0034] 110a:第一表面

[0035] 110b:第三表面

[0036] 110c:第一边缘

[0037] 111:第一基板

[0038] 711a:微结构

[0039] 112:元件层

[0040] 113:第一接垫

[0041] 114:第二接垫

[0042] 115:导线

[0043] T:主动元件

[0044] S:源极

[0045] D:漏极

[0046] G:栅极

[0047] CH:通道层

[0048] 120:第一保护层

- [0049] 121:第一导通孔

- [0050] 120a:开口

- [0051] 120b:第一开口

- [0052] 120c:第二开口

- [0053] 130:第二线路板

- [0054] 130a:第二表面

- [0055] 130b:第四表面

- [0056] 130c:第二边缘

- [0057] 131:第二基板

- [0058] 132:线路层

- [0059] 133:绝缘层

- [0060] 134:压合接垫

- [0061] 140:第二保护层

- [0062] 141:第二导通孔

- [0063] 140a:开口

- [0064] 140b:压合开口

- [0065] 150:粘着层

- [0066] 150c:粘着边缘

- [0067] 150h:厚度

- [0068] 151、453:粘着材料

- [0069] 452、552、652:框胶

- [0070] 160:连接电极

- [0071] 160h:厚度

- [0072] 270:电极保护层

- [0073] FS:平整面

- [0074] R:边缘区

- [0075] S1、S2、S3、S4、S5:步骤

- [0076] 800:显示装置

- [0077] 810: 微型发光元件

- [0078] 830:电路板FPC

- [0079] 90:切割装置

### 具体实施方式

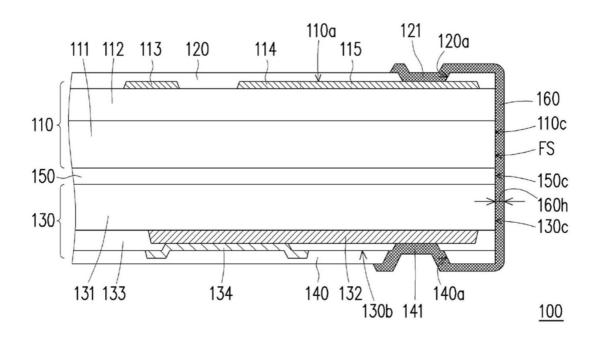

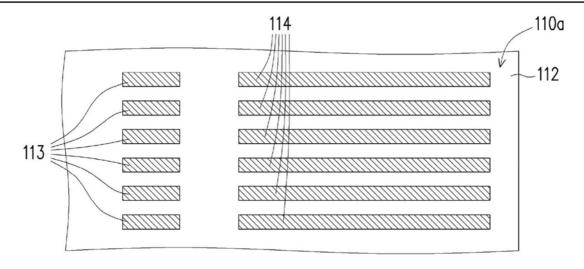

[0080] 图1A是依照本发明的第一实施例的一种阵列基板的制造方法的流程图。图1B至图 1H是依照本发明的第一实施例的一种阵列基板的制造方法的部分剖面示意图。图1I是依照本发明的第一实施例的一种阵列基板的部分制造方法的部分俯视图。图1J是依照本发明的第一实施例的一种阵列基板的部分制造方法的立体示意图。

[0081] 请参照图1A与图1B。在步骤S1中,提供第一线路板110,第一线路板110包括至少一第一接垫113以及至少一第二接垫114。举例而言,第一线路板110具有彼此相对的第一表面

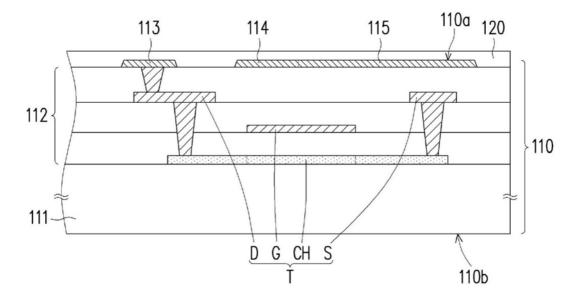

110a及第三表面110b。第一线路板110可以包括第一基板111、元件层112、第一接垫113及第二接垫114。元件层112位于第一基板111上,第一接垫113以及第二接垫114位于元件层112上,且第一接垫113与第二接垫114可以与其他的电子元件(如:主动元件T或导线115)电性连接。

[0082] 第一基板111的材质可以为玻璃、石英、有机聚合物或其他适宜被切割的绝缘材质,于本发明中并不加以限制。

[0083] 元件层112可以包括主动元件T、无源元件(未示出)或对应的导线(如:扫描线、数据线或其他类似的信号线)。举例而言,元件层112可以包括至少一主动元件T,其中第一接垫113与主动元件T电性连接,以接收主动元件T所传递的对应电压。主动元件T包括源极S、漏极D、栅极G以及通道层CH。栅极G可以与扫描线(未示出)电性连接。源极S可以与数据线(未示出)电性连接。在本实施例中,主动元件T例如为低温多晶硅薄膜晶体管(Low temperture poly Si thin film transistor;LTPS TFT),于本发明中并不加以限制。

[0084] 另外,在图1B的第一线路板110中,仅示例性地示出了一个主动元件T、一个第一接垫113及一个第二接垫114,但本发明对于第一线路板110中的主动元件T、第一接垫113及/或第二接垫114的个数并不加以限制。举例而言,如图1I所示,其中图1I可以是图1B所示出的第一线路板110的部分俯视图,在图1I中,第一线路板110可以包括多个第一接垫113及多个第二接垫114,且各个第一接垫113可以与元件层112中对应的主动元件T电性连接。

[0085] 另外,在后续的附图中,为了清楚表示,可能省略示出了元件层112中全部或部分的构件(如:主动元件T)。

[0086] 在本实施例中,可以于第一线路板110的第一表面110a上形成第一保护层120。在后续的工艺中,第一接垫113以及多个第二接垫114可以通过第一保护层120的保护而降低受损的可能。

[0087] 在本实施例中,元件层112内的元件(如:主动元件T)、第一接垫113、第二接垫114、导线115及/或第一保护层120(若有)可以通过一般的半导体或封装工艺所形成,故于此不加以赘述。

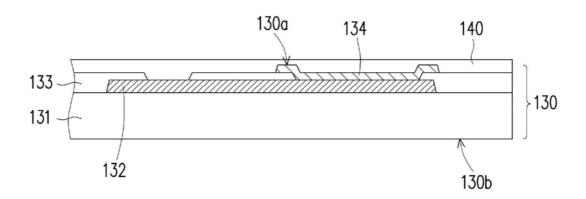

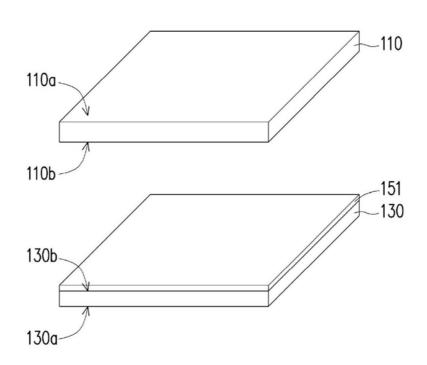

[0088] 请参照图1A与图1C。在步骤S2中,提供第二线路板130,第二线路板130包括至少一压合接垫134。举例而言,第二线路板130具有彼此相对的第二表面130a及第四表面130b。第二线路板130可以包括第二基板131、线路层132、绝缘层133及压合接垫134。

[0089] 第二基板131的材质可以为玻璃、石英、有机聚合物或其他适宜被切割的绝缘材质,于本发明中并不加以限制。

[0090] 线路层132及绝缘层133位于第二基板131上。压合接垫134可以贯穿最远离第二基板131的绝缘层133,以与线路层132电性连接。在本实施例中,压合接垫134例如为凸块底金属(Under Bump Metallurgy;UBM),但本发明不限于此。

[0091] 另外,在图1C的第二线路板130中,仅示例性地示出了一个线路层132、一个绝缘层133及一个压合接垫134,但本发明对于第二线路板130中的线路层132、绝缘层133及/或压合接垫134的个数并不加以限制。

[0092] 在本实施例中,可以于第二线路板130的第二表面130a上形成第二保护层140。在后续的工艺中,位于第二表面130a上的压合接垫134可以通过第二保护层140的保护而降低受损的可能。

[0093] 在本实施例中,线路层132、绝缘层133、压合接垫134及/或第二保护层140(若有)可以通过一般的半导体或封装工艺所形成,故于此不加以赘述。

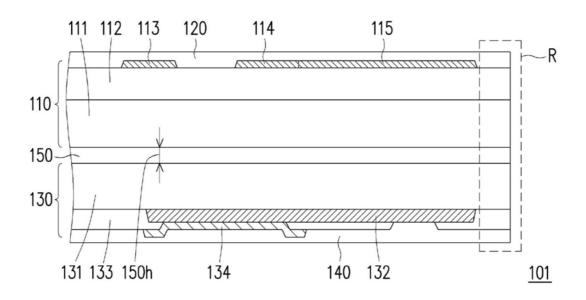

[0094] 请参照图1A、图1D与图1J。在步骤S3中,进行一粘合工艺,以形成粘合第一线路板110与第二线路板130的粘着层150。粘着层150的材质例如可以是树脂材料,但本发明不限于此。

[0095] 举例而言,如图1J所示,将第一线路板110与第二线路板130粘合的方式例如是先将如1C所示的第二线路板130上下翻转(upside down)。然后,将未固化的粘着材料151(如:树脂或胶材)涂布于第二线路板130的第四表面130b上。接着,使第一线路板110的第三表面110b上及第二线路板130的第四表面130b分别接触粘着材料151的相对两侧。之后,进行固化工艺使得粘着材料151固化,以形成如图1D所示,具有以粘着层150将第一线路板110与第二线路板130相粘合的粘合结构101。

[0096] 在其他未示出的实施例中,也可以将如1B所示的第一线路板110上下翻转。然后,将未固化的粘着材料151涂布于第一线路板110的第三表面110b上。之后,通过类似的方式以形成具有以粘着层150将第一线路板110与第二线路板130相粘合的粘合结构101。

[0097] 在其他可行的实施例中,也可以先将其他类型的粘着材料(如:双面胶)形成于第一线路板110的第三表面110b上及/或第二线路板130的第四表面130b上。然后,将第一线路板110或第二线路板130上下翻转。之后,使第一线路板110的第三表面110b上及第二线路板130的第四表面130b彼此面对面(face to face)贴合,而使第一线路板110的第三表面110b上与第二线路板130的第四表面130b之间的粘着材料形成粘着层150,以形成具有以粘着层150将第一线路板110与第二线路板130相粘合的粘合结构101。

[0098] 在本实施例中,粘着层150的厚度150h小于或等于10微米 (micrometer; μm),且大于0微米。如此一来,可以使粘着层150适宜被切割。并且,在后续的工艺 (如:将粘合结构101翻转、传送或其他类似的工艺)中,粘着层150的厚度150h小于或等于10微米可以降低第一线路板110与第二线路板130之间的剪力 (shear force),而可以降低第一线路板110及/或第二线路板130损坏的可能。

[0099] 请参照图1A、图1D至图1F。在步骤S4中,进行一切割工艺,以切割第一线路板110、粘着层150以及第二线路板130的至少其中之一。举例而言,如图1E所示,可以通过切割装置90,以激光切割、水刀切割或其他适宜的切割方式,对如1D所示的粘合结构101(示出于图1D)的边缘区R进行切割,以切割第一线路板110的第一基板111、粘着层150以及第二线路板130的第二基板131的至少其中之一。

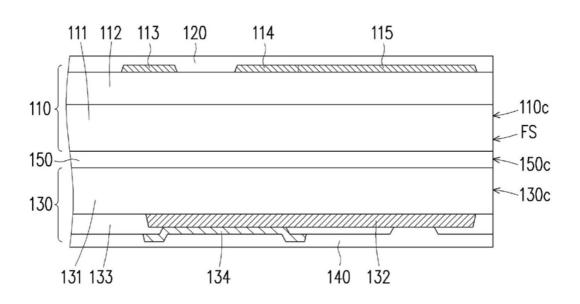

[0100] 在一些实施例中,于进行前述的切割工艺之后,可以进一步地对第一线路板110的第一边缘110c(示出于图1F)、第二线路板130的第二边缘130c(示出于图1F)以及粘着层150的粘着边缘150c(示出于图1F)进行微蚀刻(micro-etching)、研磨(polishing)或其他适宜的平整化工艺,以提升由第一基板111的第一边缘110c的表面、第二基板131的第二边缘130c的表面及粘着层150的粘着边缘150c的表面所构成的表面的平整度(flatness)。

[0101] 请参照图1F,于进行切割工艺之后,第一基板111的第一边缘110c、第二基板131的第二边缘130c以及粘着层150的粘着边缘150c基本上彼此切齐,且位于第一基板111的第一边缘110c的表面、位于第二基板131的第二边缘130c的表面以及位于粘着层150的粘着边缘150c的表面可以彼此共面(coplaner)而构成一平整面FS。

[0102] 当然,在微观尺寸(如:纳米尺寸或原子尺寸)下,任何物体的表面皆会有粗糙度,仅是相对大小的问题。因此,只要于进行切割工艺之后,位于第一基板111的第一边缘110c的表面、位于第二基板131的第二边缘130c的表面以及位于粘着层150的粘着边缘150c的表面所对应构成的一平面(如:一数学上理想的虚拟平整面),而在前述平面的法线方向上,位于第一基板111的第一边缘110c的表面、位于第二基板131的第二边缘130c的表面以及位于粘着层150的粘着边缘150c的表面相对于前述平面的最高点和最低点之间的差值(即,前述平面的平整度)小于后续形成于其上的连接电极160(示出于图1H)最小厚度160h(示出于图1H),则为本文中所定义的平整面的均等范围所涵盖。

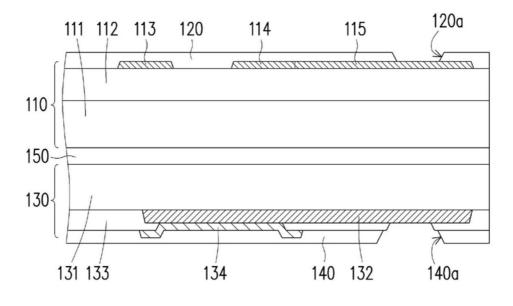

[0103] 请参照图1G。在一些实施例中,可以通过蚀刻、机械钻孔、激光钻孔或其他适宜的方式,以在第一保护层120(若有)上形成开口120a,且开口120a可以暴露出部分的导线115或其他可以与第二接垫114电性连接的一导电接垫。或是,可以通过蚀刻、机械钻孔、激光钻孔或其他适宜的方式,以在第二保护层140(若有)上形成开口140a,且开口140a可以暴露出部分的线路层132或其他可以与线路层132电性连接的另一导电接垫。

[0104] 请参照图1H,形成连接电极160,以电性连接第二接垫114与压合接垫134,连接电极160至少部分覆盖于第一基板111的第一边缘110c、第二基板131的第二边缘130c以及粘着层150的粘着边缘150c。举例而言,例如可以通过印刷(如:网印)、镀覆(如:溅镀、蒸镀)或其他适宜的方式,将导电材料至少形成在第一基板111的第一边缘110c的表面、第二基板131的第二边缘130c的表面及粘着层150的粘着边缘150c的表面所构成的表面上,以使第二接垫114可以与对应的压合接垫134电性连接。

[0105] 在一些实施例中,用于形成连接电极160的导电材料可以进一步地部分覆盖于第一线路板110的第一表面110a上,且填入第一保护层120的多个开口120a,以形成第一导通孔121。如此一来,可使第二接垫114可以通过对应的第一导通孔121及对应的连接电极160而与对应的压合接垫134电性连接。

[0106] 在一些实施例中,用于形成连接电极160的导电材料可以进一步地部分覆盖于第二线路板130的第二表面130a上,且填入第二保护层140的多个开口140a,以形成第二导通孔141。如此一来,可使第二接垫114可以通过对应的连接电极160及对应的第二导通孔141而与对应的压合接垫134电性连接。

[0107] 经过上述工艺后即可大致上完成本实施例的阵列基板100的制作。上述的阵列基板100包括第一线路板110、第二线路板130、粘着层150以及至少一连接电极160。第一线路板110具有第一表面110a,且第一线路板110包括至少一第一接垫113以及至少一第二接垫114。第二线路板130具有第二表面130a,且第二线路板130包括至少一压合接垫134。粘着层150位于第一线路板110与第二线路板130之间。第一线路板110的第一边缘110c、第二线路板130的第二边缘130c以及粘着层150的粘着边缘150c基本上彼此切齐。连接电极160可以从第一线路板110的第一表面110a沿第一线路板110的第一边缘110c、第二线路板130的第二边缘130c以及粘着层150的粘着边缘150c延伸至第二线路板130的第二表面130a。连接电极160电性连接于第二接垫114与压合接垫134。

[0108] 在本实施例中,第一线路板110的第一边缘110c的表面、第二线路板130的第二边缘130c的表面以及粘着层150的粘着边缘150c的表面构成一平整面FS,且连接电极160至少部分覆盖于平整面上。

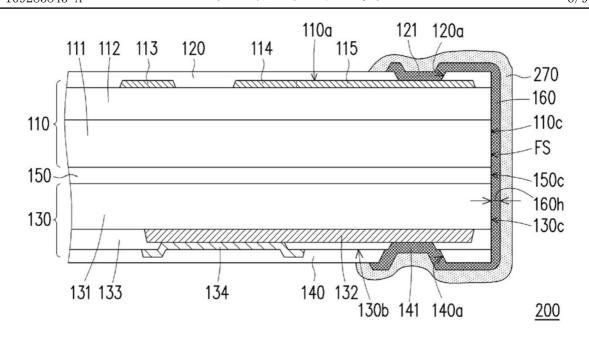

[0109] 图2是依照本发明的第二实施例的一种阵列基板的部分剖面示意图。本实施例的阵列基板200与第一实施例的阵列基板100类似,差别在于:阵列基板100还包括电极保护层270。电极保护层270覆盖连接电极160上,而可以在后续的工艺(如:将阵列基板200翻转、传送或其他类似的工艺)中可以降低连接电极160受损的可能。

[0110] 在本实施例中,可以在形成连接电极160之后,通过一般的半导体或封装工艺形成由聚合物材料、氧化硅层、氮化硅层、氮氧化硅层或是由其他适宜的介电材料所形成的电极保护层270,故于此不加以赘述。

[0111] 图3是依照本发明的第三实施例的一种阵列基板的部分剖面示意图。本实施例的阵列基板300与第二实施例的阵列基板200类似,差别在于:第一保护层120具有对应于第一接垫113的第一开口120b以及对应于第二接垫114的第二开口120c,且第二保护层140具有对应于压合接垫134的个压合开口140b。

[0112] 第一开口120b及/或第二开口120c可以通过蚀刻、机械钻孔、激光钻孔或其他适宜的方式形成,且本发明对于开口120a、第一开口120b及第二开口120c的形成顺序并不加以限制。举例而言,第一开口120b及/或第二开口120c可以在与开口120a相同的工艺中形成。

[0113] 压合开口140b可以通过蚀刻、机械钻孔、激光钻孔或其他适宜的方式形成,且本发明对于压合开口140b及开口140a的形成顺序并不加以限制。举例而言,压合开口140b可以在与开口140a相同的工艺中形成。

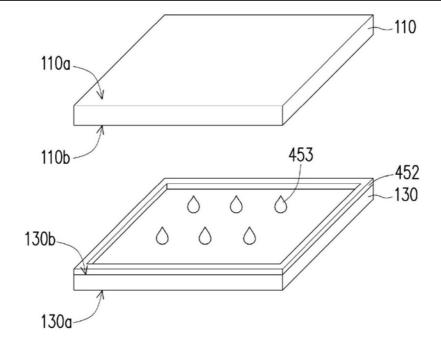

[0114] 图4是依照本发明的第四实施例的一种阵列基板的部分制造方法的立体示意图。 具体而言,图4可以为图1A中的步骤S3中,所进行的粘合工艺的立体示意图。

[0115] 在本实施例中,将第一线路板110与第二线路板130黏合的方式例如是先将如1C所示的第二线路板130上下翻转。然后在第二线路的第四表面130b上形成框胶452后,将未固化的粘着材料453涂布于第二线路板130的第四表面130b上且于框胶452所围绕的范围内。接着,使第一线路板110的第三表面110b上及第二线路板130的第四表面130b分别接触粘着材料453的相对两侧。之后,进行固化工艺使得粘着材料453固化,以形成类似于如图1D所示的粘合结构101。

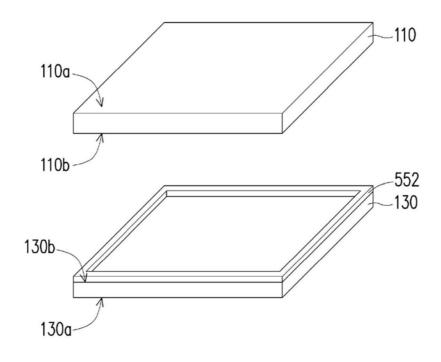

[0116] 图5是依照本发明的第五实施例的一种阵列基板的部分制造方法的立体示意图。 具体而言,图5可以为图1A中的步骤S3中,所进行的粘合工艺的立体示意图。

[0117] 在本实施例中,将第一线路板110与第二线路板130粘合的方式例如是先将如1C所示的第二线路板130上下翻转。然后在第二线路板130的第四表面130b上形成框胶552后。接着,于一低气压(如:低于1大气压)的环境下,使第一线路板110的第三表面110b上及第二线路板130的第四表面130b分别接触框胶552的相对两侧。之后,于室压(如:1大气压)的环境,可以通过框胶552及外界的大气压力使第一线路板110的第三表面110b与第二线路板130的第四表面130b分别与框胶的相对两侧密合,以形成类似于如图1D所示的粘合结构101。

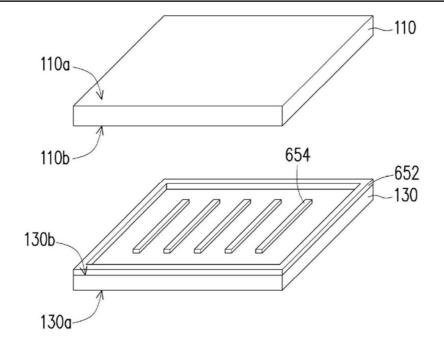

[0118] 图6是依照本发明的第六实施例的一种阵列基板的部分制造方法的立体示意图。 具体而言,图6可以为图1A中的步骤S3中,所进行的粘合工艺的立体示意图。

[0119] 在本实施例中,将第一线路板110与第二线路板130粘合的方式例如是先将如1C所示的第二线路板130上下翻转。然后在第二线路板130的第四表面130b上形成框胶652后,于框胶652所围绕的范围内形成粘着材料654(如:双面胶条)。接着,使第一线路板110的第三表面110b上及第二线路板130的第四表面130b分别接触框胶652及/或粘着材料654的相对

两侧,以形成类似于如图1D所示的粘合结构101。

[0120] 图7是依照本发明的第七实施例的一种阵列基板的部分剖面示意图。本实施例的阵列基板700与第一实施例的阵列基板100类似,差别在于:第一线路板110的第三表面110b(即,第一基板111远离元件层112且与粘着层150相接处的表面)上可以更具有多个微结构711a。位于第三表面110b上的微结构可以提升第一线路板110与粘着层150之间的粘着力。

[0121] 在其他未示出的实施例中,第二线路板130的第四表面130b(即,第二基板131远离元件层112且与粘着层150相接处的表面)可以更具有类似的微结构(如:图7中的微结构711a),于本发明中并不加以限制。

[0122] 基于上述,本发明的阵列基板是通过粘着层将第一线路板与第二线路板彼此粘合。因此,阵列基板的制造方法较为简单。并且,可以在将第一线路板与第二线路板彼此粘合前确认第一线路板与第二线路板具有良好的功能。因此,可以提升阵列基板的制作良率。另外,用于将第一线路板与第二线路板彼此电性连接的连接电极是形成在第一线路板的第一边缘、第二线路板的第二边缘以及粘着层的粘着边缘上,而第一线路板的第一边缘、第二线路板的第二边缘以及粘着层的粘着边缘上可以通过切割工艺而基本上彼此切齐。因此,阵列基板的制造方法较为简单,且可以提升阵列基板的制作良率。

[0123] 本发明的阵列基板100、200、300、700或其他类似的阵列基板可以依据设计上的需求而有不同的应用,本发明对于阵列基板100、200、300、700或其他类似的阵列基板的应用方式并不加以限制。

[0124] 图8是依照本发明的一种显示装置的部分剖面示意图。显示装置800可以包括阵列基板300以及微型发光元件810,且微型发光元件810电性连接于对应的第一接垫113以及对应的第二接垫114。

[0125] 在本实施例中,显示装置800所包括的阵列基板300是以第三实施例的阵列基板300为例。在其他的实施例中,显示装置800也可以包括前述任一实施例的阵列基板(如:阵列基板100、200、300、700)或包括类似于前述任一实施例的阵列基板。

[0126] 在本实施例中,例如可以将微型发光元件810配置于阵列基板300上,且通过覆晶接合(flip-chip bonding)的方式而使微型发光元件810通过对应的导电端子820电性连接至对应的第一接垫113以及对应的第二接垫114。但本发明对于微型发光元件810与阵列基板300之间的电性连接方式并不加以限制。在一些未示出的实施例中,微型发光元件810可以通过导线以与阵列基板300电性连接。

[0127] 在本实施例中,显示装置800可以还包括电路板830。电路板830可以通过导电端子840电性连接于压合接垫134。电路板830例如为柔性印刷电路板(Flexible Printed Circuit;FPC),但本发明不限于此。

[0128] 前述实施例的微型发光元件810的尺寸例如小于100微米,优选地,小于50微米,但大于0微米。微型发光元件810可例如是有机发光元件或无机发光元件,优选地,可为无机发光元件,但不限于此。微型发光元件810的结构可为P-N二极管、P-I-N二极管、或其它合适的结构。微型发光元件810的类型可以是垂直式微型发光元件、水平式微型发光元件或者是覆晶式微型发光元件。微型发光元件810可为有机材料(例如:有机高分子发光材料、有机小分子发光材料、有机配合物发光材料、或其它合适的材料、或前述材料的组合)、无机材料(例如:钙钛矿材料、稀土离子发光材料、稀土荧光材料、半导体发光材料、或其它合适的材料、

或前述材料的组合)、或其它合适的材料、或前述材料的组合。

[0129] 前述实施例中,主动元件T可采用薄膜晶体管(TFT),例如底闸型晶体管、顶闸型晶体管、立体型晶体管、或其它合适的晶体管。底闸型的晶体管的栅极G位于半导体层(如:通道层CH)的下方,顶闸型晶体管的栅极G或位于半导体层(如:通道层CH)的上方,而立体型晶体管的半导体层通道延伸非位于一平面。半导体层(如:通道层CH)可为单层或多层结构,且其材料包含非晶硅、微晶硅、纳米晶硅、多晶硅、单晶硅、有机半导体材料、氧化物半导体材料、纳米碳管/杆、钙钛矿材料、或其它合适的材料或前述的组合。

[0130] 此外,可将前述实施例的主动元件T与另一主动元件(未示出)及电容(未示出)电性连接,简称为两个主动元件与一个电容(可表示为2T1C)。于其他实施例中,每个微型发光元件810所对应的主动元件与电容的个数可依设计变更,而可例如被简称为三个主动元件和一个或两个电容(可表示为3T1C/2C)、四个主动元件和一个或两个电容(可表示为4T1C/2C)、五个主动元件和一个或两个电容(可表示为5T1C/2C)、六个主动元件和一个或两个电容(可表示为6T1C/2C)、或是其他适合的电路配置。

[0131] 基于上述,本发明的显示装置是由本发明的阵列基板所构成。因此,显示装置的制造方法也可以较为简单,且具有优选的制作良率。

[0132] 综上所述,本发明的阵列基板的制造方法较为简单,且具有优选的制作良率。因此,通过本发明的阵列基板所构成的显示装置的制造方法也可以较为简单,且具有优选的制作良率。

[0133] 虽然本发明已以实施例公开如上,然其并非用以限定本发明,任何所属技术领域中技术人员,在不脱离本发明的构思和范围内,当可作些许的变动与润饰,故本发明的保护范围当视权利要求所界定者为准。

图1A

图1B

图1C

图1D

图1E

图1F

图1G

图1H

图1I

图1J

图2

图3

图5

图6

图7

图8

| 专利名称(译)        | 阵列基板、应用其的显示装置及该基板和装置制造方法          |         |            |  |

|----------------|-----------------------------------|---------|------------|--|

| 公开(公告)号        | CN109285845A                      | 公开(公告)日 | 2019-01-29 |  |

| 申请号            | CN201811317754.4                  | 申请日     | 2018-11-07 |  |

| [标]申请(专利权)人(译) | 友达光电股份有限公司                        |         |            |  |

| 申请(专利权)人(译)    | 友达光电股份有限公司                        |         |            |  |

| 当前申请(专利权)人(译)  | 友达光电股份有限公司                        |         |            |  |

| [标]发明人         | 林宜欣<br>黄朝伟<br>陈正欣                 |         |            |  |

| 发明人            | 林宜欣<br>黄朝伟<br>陈正欣                 |         |            |  |

| IPC分类号         | H01L27/12 H01L21/77 H01L27/15     |         |            |  |

| CPC分类号         | H01L27/124 H01L27/1259 H01L27/156 |         |            |  |

| 代理人(译)         | 黄艳                                |         |            |  |

| 优先权            | 107127056 2018-08-03 TW           |         |            |  |

| 外部链接           | Espacenet SIPO                    |         |            |  |

# 摘要(译)

一种阵列基板,其包括第一线路板、第二线路板、粘着层以及至少一连接电极。第一线路板具有第一表面。第一线路板包括至少一第一接垫以及至少一第二接垫。第二线路板具有第二表面。第二线路板包括至少一压合接垫。粘着层位于第一线路板与第二线路板之间。第一线路板的第一边缘、第二线路板的第二边缘以及粘着层的粘着边缘基本上彼此切齐。连接电极从第一表面沿第一边缘、第二边缘以及粘着边缘延伸至第二表面。连接电极电性连接于第二接垫与压合接垫。